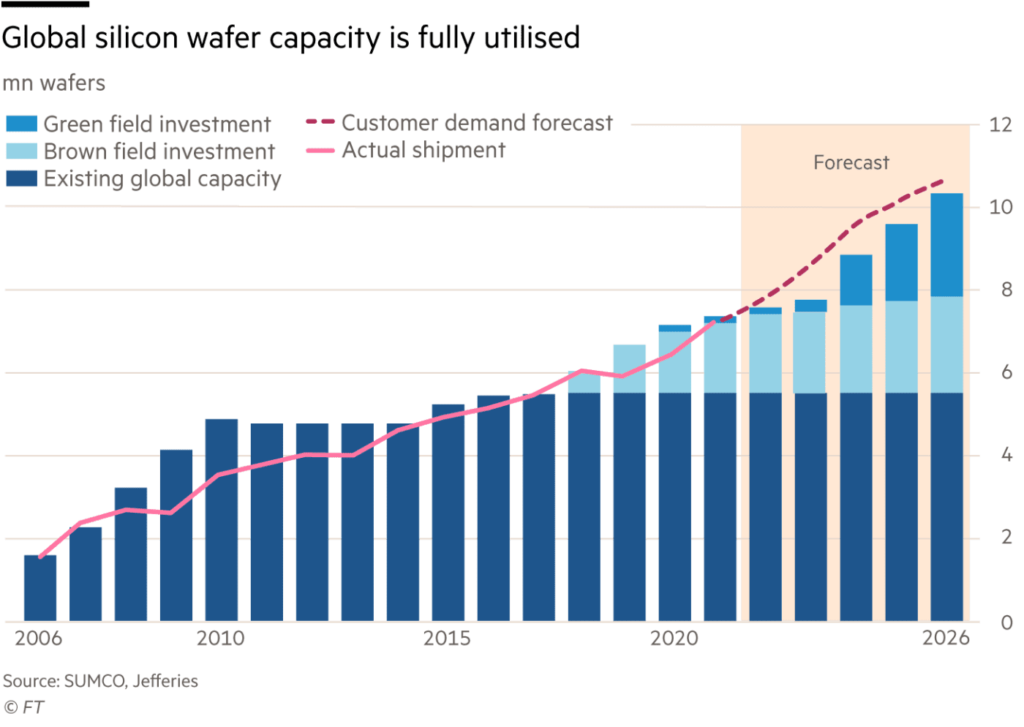

This is the third and final blog in a short series of posts looking at the chip shortage crisis our industry is facing. Previous posts looked at the political situations both affecting and attempting to tackle the problems, and how the chip makers are ramping up and investing in their own attempts to sensibly fill the supply gaps and maximize on the opportunities as quickly as possible.

In a previous recent blog, I’ve set out some thoughts on the realities and impacts of chip shortages on the evolving connected car market.

S&P are scaling back forecasts on car production for 2022, given the chip supply issue affecting the industry. Automotive industry impact: ‘Toyota and Nissan, have scaled back production and others such as BMW, Ford and Volvo have removed certain features from some cars to enable them to continue production.’

In the mobile phone markets, Samsung and Apple have been using their might to maintain their own supplies…but other OEMs have been left struggling

“low-end OEMs…struggled the most to adapt with chip foundries expected to take “years” to spool up to demand.” https://www.androidpolice.com/apple-and-samsungs-smartphone-businesses-are-surviving-the-global-chip-shortage-in-ways-only-they-can/

In the face of chip shortages and times of geopolitical uncertainty, shortages will continue in the short to mid-term at least, so OEMs looking to remain competitive will need to continually assess their options and consider moving or duplicating (second-sourcing) designs to secure capacity from more than one manufacturing partner.

Some Tier 2 fabs are positioned ready to seize the opportunities in these times of uncertainty – they can offer attractive costs and potentially be more responsive and adaptable to customer needs.

Migrating IP to other fabs, design nodes or process technologies can be complex and, itself, time-consuming (hence competitively prohibitive) unless it’s done with the right tools. That is where we at Thalia can help. For 2022 and possibly into next year we need to help our customers reduce their costs in IP migration through innovative IP reuse, and help to maintain their competitive edge.